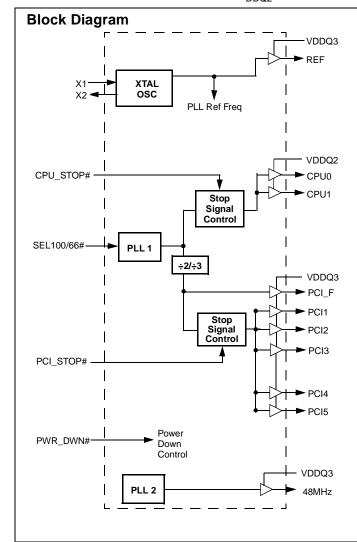

# 100-MHz Mobile Motherboard System Clock

#### **Features**

- Maximized EMI suppression using Cypress's Spread Spectrum technology

- · Power-on default to spread mode

- Two copies of CPU output

- Six copies of PCI output (synchronous w/CPU outputs)

- One copy of 48-MHz USB output

- One Buffered copy of 14.318-MHz input reference signal

- Supports 100-MHz or 66-MHz CPU operation

- Power management control input pins

- Low Frequency Test Mode

- · Available in 28-pin SSOP (209 mil)

#### **Key Specifications**

Supply Voltages: .....  $V_{DDQ3} = 3.3V \pm 5\%$  $V_{DDQ2} = 2.5V \pm 5\%$

| CPU0:1 Skew:175 ps                                              |

|-----------------------------------------------------------------|

| CPU0:1 Cycle-to-Cycle Jitter:200 ps                             |

| PCI_F, PCI1:5 Skew:500 ps                                       |

| PCI_F, PCI1:5 Cycle-to-Cycle Jitter:250 ps                      |

| CPU to PCI Skew: 1.5 to 4.0 ns (CPU Leads)                      |

| Output Duty Cycle:                                              |

| PCI_F, PCI Edge Rate:≥1 V/ns                                    |

| CPU_STOP#, PWR_DWN#, PCI_STOP#: 250-k $\Omega$ pull-up resistor |

Table 1. Pin Selectable Frequency

| SEL100/66# | CPU(0:1) | PCI  | Spread% |

|------------|----------|------|---------|

| 0          | 66.6 MHz | 33.3 | -0.5%   |

| 1          | 100 MHz  | 33.3 | -0.5%   |

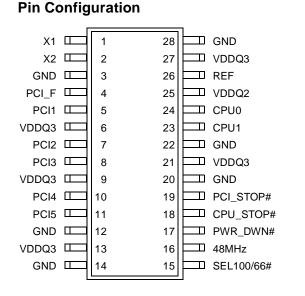

# **Pin Definitions**

| Pin Name   | Pin<br>No.               | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU0:1     | 24, 23                   | 0           | CPU Clock Outputs 0 and 1: These two CPU clock outputs are controlled by the CPU_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ2. Frequency of signals is set by SEL100/66# input.                                                                                                                                                |

| PCI1:5     | 5, 7, 8, 10,<br>11       | 0           | <b>PCI Bus Clock Outputs 1 through 5:</b> These five PCI clock outputs are controlled by the PCI_STOP# control pin. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                 |

| PCI_F      | 4                        | 0           | <b>Fixed PCI Clock Output:</b> Unlike PCI1:5 outputs, this output is not controlled by the PCI_STOP# control pin; it cannot be forced LOW by PCI_STOP#. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                             |

| 48MHz      | 16                       | 0           | <b>48-MHz Output:</b> Fixed clock output at 48 MHz. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                 |

| CPU_STOP#  | 18                       | I           | CPU_STOP# Input: When brought LOW, clock outputs CPU0:1 are stopped LOW after completing a full clock cycle (2–3 CPU clock latency). When brought HIGH, clock outputs CPU0:1 start with a full clock cycle (2–3 CPU clock latency).                                                                                                                                 |

| PCI_STOP#  | 19                       | I           | <b>PCI_STOP# Input:</b> The PCI_STOP# input enables the PCI1:5 outputs when HIGH and causes them to remain at logic 0 when LOW. The PCI_STOP signal is latched on the rising edge of PCI_F. Its effect takes place on the next PCI_F clock cycle.                                                                                                                   |

| REF        | 26                       | 0           | Fixed 14.318-MHz Output: Used for various system applications. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                      |

| SEL100/66# | 15                       | I           | Frequency Selection Inputs: Select power-up default CPU clock frequency as shown in Table 1 on page 1.                                                                                                                                                                                                                                                              |

| X1         | 1                        | I           | Crystal Connection or External Reference Frequency Input: This pin can either be used as a connection to a crystal or to a reference signal.                                                                                                                                                                                                                        |

| X2         | 2                        | I           | <b>Crystal Connection:</b> An input connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                               |

| PWR_DWN#   | 17                       | I           | <b>Power-Down Control:</b> When this input is LOW, device goes into a low-power stand-by condition. All outputs are held LOW. CPU and PCI clock outputs are stopped LOW after completing a full clock cycle (2–3 CPU clock cycle latency). When brought HIGH, CPU and PCI outputs start with a full clock cycle at full operating frequency (3 ms maximum latency). |

| VDDQ3      | 6, 9, 13, 21,<br>27      | Р           | Power Connection: Connected to 3.3V supply.                                                                                                                                                                                                                                                                                                                         |

| VDDQ2      | 25                       | Р           | Power Connection: Power supply for CPU0:1 output buffer. Connected to 2.5V.                                                                                                                                                                                                                                                                                         |

| GND        | 3, 12, 14, 20,<br>22, 28 | G           | Ground Connection: Connect all ground pins to the common system ground plane.                                                                                                                                                                                                                                                                                       |

#### **Spread Spectrum Feature**

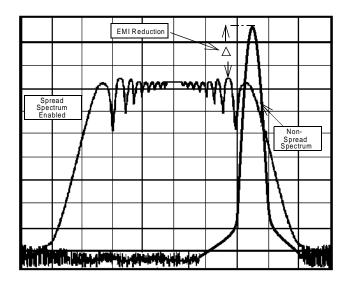

The device generates a clock that is frequency modulated in order to increase the bandwidth that it occupies. By increasing the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in *Figure 1*.

As shown in *Figure 1*, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction is:

$$dB = 6.5 + 9*log_{10}(P) + 9*log_{10}(F)$$

Where P is the percentage of deviation and F is the frequency in MHz where the reduction is measured.

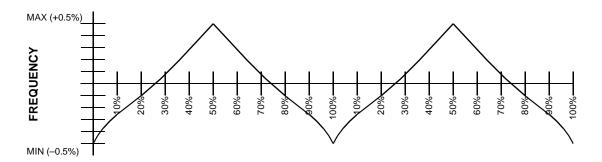

The output clock is modulated with a waveform depicted in Figure 2. This waveform, as discussed in "Spread Spectrum Clock Generation for the Reduction of Radiated Emissions" by Bush, Fessler, and Hardin produces the maximum reduction in the amplitude of radiated electromagnetic emissions. The deviation selected for this chip is -0.5% of the center frequency. Figure 2 details the Cypress spreading pattern. Cypress does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on these devices.

Figure 1. Typical Clock and SSFTG Comparison

Figure 2. Typical Modulation Profile

#### **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

| ESD <sub>PROT</sub>               | Input ESD Protection                   | 2 (min.)     | kV   |

# **DC Electrical Characteristics:** $T_A = 0$ °C to +70°C, $V_{DDQ3} = 3.3V \pm 5\%$ , $V_{DDQ2} = 2.5V \pm 5\%$ , CPU0:1 = 66.6/100 MHz

| Parameter           | Descriptio                                | Test Condition                    | Min.                          | Тур.      | Max. | Unit                  |    |

|---------------------|-------------------------------------------|-----------------------------------|-------------------------------|-----------|------|-----------------------|----|

| Supply Cur          | rent                                      |                                   | -                             | •         |      |                       |    |

| I <sub>DD</sub>     | 3.3V Supply Current                       |                                   | Outputs Loaded <sup>[1]</sup> |           |      | 75                    | mA |

| I <sub>DD</sub> 2.5 | 2.5V Supply Current                       |                                   | Outputs Loaded <sup>[1]</sup> |           |      | 50                    | mA |

| Logic Input         | s                                         |                                   |                               |           |      |                       |    |

| V <sub>IL</sub>     | Input Low Voltage                         |                                   |                               | GND - 0.3 |      | 0.8                   | V  |

| V <sub>IH</sub>     | Input High Voltage                        |                                   |                               | 2.0       |      | V <sub>DD</sub> + 0.3 | V  |

| I <sub>IL</sub>     | Input Low Current <sup>[2]</sup>          |                                   |                               |           |      | -25                   | μA |

| I <sub>IH</sub>     | Input High Current <sup>[2]</sup>         |                                   |                               |           |      | 10                    | μA |

| I <sub>IL</sub>     | Input Low Current (SEL100/6               | 6#)                               |                               |           |      | <b>-</b> 5            | μA |

| I <sub>IH</sub>     | Input High Current (SEL100/6              | 6#)                               |                               |           |      | 5                     | μA |

| Clock Outp          | uts                                       |                                   |                               | •         |      |                       |    |

| V <sub>OL</sub>     | Output Low Voltage                        |                                   | I <sub>OL</sub> = 1 mA        |           |      | 50                    | mV |

| V <sub>OH</sub>     | Output High Voltage                       |                                   | $I_{OH} = -1 \text{ mA}$      | 3.1       |      |                       | V  |

| V <sub>OH</sub>     | Output High Voltage                       | CPU0:1                            | I <sub>OH</sub> = −1 mA       | 2.2       |      |                       | V  |

| I <sub>OL</sub>     | Output Low Current                        | CPU0:1                            | V <sub>OL</sub> = 1.25V       | 55        | 115  | 190                   | mA |

|                     |                                           | PCI1:5, _F                        | V <sub>OL</sub> = 1.5V        | 20.5      | 53   | 139                   | mA |

|                     |                                           | REF                               | V <sub>OL</sub> = 1.5V        | 25        | 37   | 76                    | mA |

| I <sub>OH</sub>     | Output High Current                       | CPU0:1                            | V <sub>OL</sub> = 1.25V       | 50        | 110  | 195                   | mA |

|                     |                                           | PCI1:5, _F                        | V <sub>OL</sub> = 1.5V        | 31        | 55   | 189                   | mA |

|                     |                                           | REFX                              | V <sub>OL</sub> = 1.5V        | 27        | 44   | 94                    | mA |

| Crystal Osc         | cillator                                  |                                   |                               |           |      |                       |    |

| V <sub>TH</sub>     | X1 Input Threshold Voltage <sup>[3]</sup> |                                   | $V_{DDQ3} = 3.3V$             |           | 1.65 |                       | V  |

| C <sub>LOAD</sub>   | Load Capacitance, as seen by              | y External Crystal <sup>[4]</sup> |                               |           | 14   |                       | pF |

| C <sub>IN,X1</sub>  | X1 Input Capacitance <sup>[5]</sup>       |                                   | Pin X2 unconnected            |           | 28   |                       | pF |

| Pin Capaci          | tance/Inductance                          |                                   |                               | •         |      |                       |    |

| C <sub>IN</sub>     | Input Pin Capacitance                     |                                   | Except X1 and X2              |           |      | 5                     | pF |

| C <sub>OUT</sub>    | Output Pin Capacitance                    |                                   |                               |           |      | 6                     | pF |

| L <sub>IN</sub>     | Input Pin Inductance                      |                                   |                               |           |      | 7                     | nΗ |

- All clock outputs loaded with 6"  $60\Omega$  transmission lines with 20-pF capacitors. CPU\_STOP#, PCI\_STOP#, and PWRDWN# logic inputs have internal pull-up resistors. X1 input threshold voltage (typical) is  $V_{DD}/2$ .

- The W48C111-17 contains an internal crystal load capacitor between pin X1 and ground and another between pin X2 and ground. Total load placed on crystal is 14 pF; this includes typical stray capacitance of short PCB traces to crystal.

X1 input capacitance is applicable when driving X1 with an external clock source (X2 is left unconnected).

#### **AC Electrical Characteristics**

## $\rm T_A = 0^{\circ}C \ to \ +70^{\circ}C, \ V_{DDQ3} = 3.3V \pm 5\%, V_{DDQ2} = 2.5V \pm 5\%, \ f_{XTL} = 14.31818 \ MHz$

AC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the clock output.

#### CPU Clock Outputs, CPU0:1 (Lump Capacitance Test Load = 20 pF)

|                 |                                                    |                                                                                                                     | CPU = 66.6 MHz |      |      | = 100 | MHz  |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------|------|------|-------|------|------|------|

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | Min.           | Тур. | Max. | Min.  | Тур. | Max. | Unit |

| t <sub>P</sub>  | Period                                             | Measured on rising edge at 1.25V                                                                                    | 15             |      | 15.5 | 10    |      | 10.5 | ns   |

| t <sub>H</sub>  | High Time                                          | Duration of clock cycle above 2.0V                                                                                  | 5.2            |      |      | 3.0   |      |      | ns   |

| t_              | Low Time                                           | Duration of clock cycle below 0.4V                                                                                  | 5.0            |      |      | 2.8   |      |      | ns   |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.0V                                                                                          | 1              |      | 4    | 1     |      | 4    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Time                              | Measured from 2.0V to 0.4V                                                                                          |                |      | 4    | 1     |      | 4    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.25V                                                                        |                |      | 55   | 45    |      | 55   | %    |

| t <sub>JC</sub> | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.25V. Maximum difference of cycle time between two adjacent cycles.                     |                |      | 200  |       |      | 250  | ps   |

| t <sub>SK</sub> | Output Skew                                        | Measured on rising edge at 1.25V                                                                                    |                |      | 175  |       |      | 175  | ps   |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |                |      | 3    |       |      | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |                | 13.5 |      |       | 13.5 |      | Ω    |

#### PCI Clock Outputs, PCI1:5 and PCI\_F (Lump Capacitance Test Load = 30 pF

|                 |                                                    |                                                                                                                     | CPU = | 66.6/10 | 00 MHz |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|---------|--------|------|

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | Min.  | Тур.    | Max.   | Unit |

| t <sub>P</sub>  | Period                                             | Measured on rising edge at 1.5V                                                                                     | 30    |         |        | ns   |

| t <sub>H</sub>  | High Time                                          | Duration of clock cycle above 2.4V                                                                                  | 12    |         |        | ns   |

| tL              | Low Time                                           | Duration of clock cycle below 0.4V                                                                                  | 12    |         |        | ns   |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 1     |         | 4      | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 1     |         | 4      | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45    |         | 55     | %    |

| t <sub>JC</sub> | Jitter, Cycle-to-Cycle                             | Measured on rising edge at 1.5V. Maximum difference of cycle time between two adjacent cycles.                      |       |         | 250    | ps   |

| t <sub>SK</sub> | Output Skew                                        | Measured on rising edge at 1.5V                                                                                     |       |         | 500    | ps   |

| t <sub>O</sub>  | CPU to PCI Clock Skew                              | Covers all CPU/PCI outputs. Measured on rising edge at 1.5V. CPU leads PCI output.                                  | 1.5   |         | 4      | ns   |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |       |         | 3      | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |       | 30      |        | Ω    |

#### REF Clock Output (Lump Capacitance Test Load = 20 pF)

|                 |                                                    |                                                                                                                     | CPU =  | CPU = 66.6/100 MHz |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|--------------------|------|------|

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | Min.   | Тур.               | Max. | Unit |

| f               | Frequency, Actual                                  | Frequency generated by crystal oscillator                                                                           | 14.318 |                    |      | MHz  |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 0.5    |                    | 2    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 0.5    |                    | 2    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45     |                    | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |        |                    | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |        | 40                 |      | Ω    |

### 48-MHz Clock Output (Lump Capacitance Test Load = 20 pF)

|                 |                                                    |                                                                                                                     | CPU  | CPU = 66.6/100 MHz |      |      |

|-----------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|--------------------|------|------|

| Parameter       | Description                                        | Test Condition/Comments                                                                                             | Min. | Тур.               | Max. | Unit |

| f               | Frequency, Actual                                  | Determined by PLL divider ratio (see m/n below)                                                                     |      | 48.008             |      | MHz  |

| f <sub>D</sub>  | Deviation from 48 MHz                              | (48.008 – 48)/48                                                                                                    |      | +167               |      | ppm  |

| m/n             | PLL Ratio                                          | (14.31818 MHz x 57/17 = 48.008 MHz)                                                                                 |      | 57/17              |      |      |

| t <sub>R</sub>  | Output Rise Edge Rate                              | Measured from 0.4V to 2.4V                                                                                          | 0.5  |                    | 2    | V/ns |

| t <sub>F</sub>  | Output Fall Edge Rate                              | Measured from 2.4V to 0.4V                                                                                          | 0.5  |                    | 2    | V/ns |

| t <sub>D</sub>  | Duty Cycle                                         | Measured on rising and falling edge at 1.5V                                                                         | 45   |                    | 55   | %    |

| f <sub>ST</sub> | Frequency Stabilization from Power-up (cold start) | Assumes full supply voltage reached within 1 ms from power-up. Short cycles exist prior to frequency stabilization. |      |                    | 3    | ms   |

| Z <sub>o</sub>  | AC Output Impedance                                | Average value during switching transition. Used for determining series termination value.                           |      | 40                 |      | Ω    |

# **Ordering Information**

| Ordering Code | Freq. Mask<br>Code | Package<br>Name | Package Type           |

|---------------|--------------------|-----------------|------------------------|

| W48C111       | -17                | Н               | 28-pin SSOP (209 mils) |

Document #:38-00843

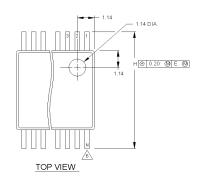

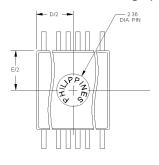

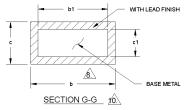

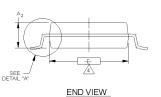

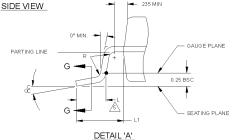

#### **Package Diagram**

#### 28-Pin Small Shrink Outline Package (SSOP, 209 mils)

#### **BOTTOM VIEW**

NOTES:

- MAXIMUM DIE THICKNESS ALLOWABLE IS 0.43mm (.017 INCHES). DIMENSIONING & TOLERANCES PER ANSI.Y14.5M-1982.

- 3. "T" IS A REFERENCE DATUM.

- , "T' IS A REFERENCE DATUMS AND DO NOT

"DOS LIDE MOLD FLASH OR PROTRUSIONS, BUT

DO INCLUDE MOLD HISAH OR PROTRUSIONS, BUT

DO INCLUDE MOLD MISMATCH AND ARE MEASURED

AT THE PARTING LINE, MOLD FLASH OR

PROTRUSIONS SHALL NOT EXCEED 0.15mm PER SIDE.

DIMENSION IS THE LENGTH OF TERMINAL

FOR SOLDERING TO A SUBSTRATE.

TERMINAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

- TERMINAL POSITIONS ARE SHOWN FOR REPERENCE UNIT.

FORMED LEADS SHALL BE PLANAR WITH RESPECT TO

ONE ANOTHER WITHIN 0.08mm AT SEATING PLANE.

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION/INTRUSION.

ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13mm TOTAL IN

EXCESS OF b DIMENSION AT MAXIMUM MATERIAL CONDITION,

DAMBAR INTRUSION SHALL NOT REDUCE DIMENSION b BY MORE

THAN 0.07mm AT LEAST MATERIAL CONDITION.

CONTROLLING DIMENSION: MILLIMETERS.

D NOM.

- 10. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 AND 0.25mm FROM LEAD TIPS.

- THIS PACKAGE OUTLINE DRAWING COMPLIES WITH JEDEC SPECIFICATION NO. MO-150 FOR THE LEAD COUNTS SHOWN

6 N

14

16 20 24

#### THIS TABLE IN MILLIMETERS

| S<br>Y         |      | COMMO     |                | NOTE           |        |  |  |  |  |

|----------------|------|-----------|----------------|----------------|--------|--|--|--|--|

| M<br>B         | DI   | MENSIO    | N <sub>O</sub> | VARI-          |        |  |  |  |  |

| 2              | MIN. | NOM.      | MAX.           | T <sub>E</sub> | ATIONS |  |  |  |  |

| Α              | 1.73 | 1.86      | 1.99           |                | AA     |  |  |  |  |

| A <sub>1</sub> | 0.05 | 0.13      | 0.21           |                | AB     |  |  |  |  |

| A <sub>2</sub> | 1.68 | 1.73      | 1.78           |                | AC     |  |  |  |  |

| b              | 0.25 | -         | 0.38           | 8,10           | AD     |  |  |  |  |

| b1             | 0.25 | 0.30      | 0.33           | 10             | AE     |  |  |  |  |

| С              | 0.09 | -         | 0.20           | 10             | AF     |  |  |  |  |

| c1             | 0.09 | 0.15      | 0.16           | 10             |        |  |  |  |  |

| D              | SEE  | VARIATION | IS             | 4              |        |  |  |  |  |

| Е              | 5.20 | 5.30      | 5.38           | 4              |        |  |  |  |  |

| е              |      | 0.65 BSC  |                |                |        |  |  |  |  |

| Н              | 7.65 | 7.80      | 7.90           |                |        |  |  |  |  |

| L              | 0.63 | 0.75      | 0.95           | 5              |        |  |  |  |  |

| L1             |      | 1.25 REF. |                |                |        |  |  |  |  |

| N              | SEE  | VARIATION | 6              |                |        |  |  |  |  |

| oc             | 0°   | 4°        | 8°             |                |        |  |  |  |  |

| R              | 0.09 | 0.15      |                |                |        |  |  |  |  |

|                |      |           | 0.00           |                |        |  |  |  |  |

#### VARIATION AF IS DESIGNED BUT NOT TOOLED

#### THIS TABLE IN INCHES

| S<br>Y<br>M    |                | COMMON    |      |                | NOTE   |      | 4    |      | 6  |

|----------------|----------------|-----------|------|----------------|--------|------|------|------|----|

| B              | DI             | MENSIO    | NS   | N <sub>O</sub> | VARI-  |      | D    |      | N  |

| 인              | MIN.           | NOM.      | MAX. | E              | ATIONS | MIN. | NOM. | MAX. |    |

| Α              | .068           | .073      | .078 |                | AA     | .239 | .244 | .249 | 14 |

| Αı             | .002           | .005      | .008 |                | AB     | .239 | .244 | .249 | 16 |

| A <sub>2</sub> | .066           | .068      | .070 |                | AC     | .278 | .284 | .289 | 20 |

| b              | .010           | -         | .015 | 8,10           | AD     | .318 | .323 | .328 | 24 |

| b1             | .010           | .012      | .013 | 10             | AE     | .397 | .402 | .407 | 28 |

| С              | .004           | -         | .008 | 10             | AF     | .397 | .402 | .407 | 30 |

| c1             | .004           | .006      | .006 | 10             |        |      |      |      |    |

| D              | SEE            | VARIATION | IS   | 4              |        |      |      |      |    |

| E              | .205           | .209      | .212 | 4              |        |      |      |      |    |

| е              |                | 0256 BSC  |      |                |        |      |      |      |    |

| Н              | .301           | .307      | .311 |                |        |      |      |      |    |

| L              | .025           | .030      | .037 | 5              |        |      |      |      |    |

| L1             | .049 REF.      |           |      |                |        |      |      |      |    |

| Ŋ              | SEE VARIATIONS |           |      | 6              |        |      |      |      |    |

| °C             | 0°             | 4°        | 8°   |                |        |      |      |      |    |

| R              | .004           | .006      |      |                |        |      |      |      |    |

|                |                |           |      |                |        |      |      |      |    |

<sup>©</sup> Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.